|

1945年,約翰•范紐曼(John Von Neumann)以顧問身份參加,

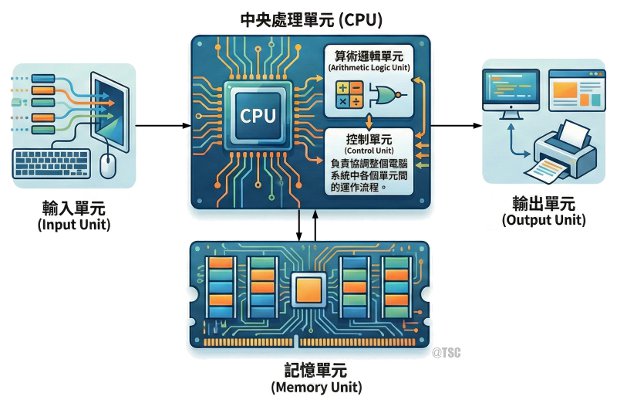

和愛克特(J.P. Eckert)和毛克萊(John Mauchly), 設計了EDVAC的計畫(和ENIAC不同,此為二進位制計算機), 在1949年,在劍橋大學的計畫,完成了 EDSAC (Electronic Delay Storage Automatic Calculator)計算機, 提出所謂內存程式(Stored Program)的架構概念, 簡單來說,就是使用記憶體來儲存計算機的指令與資料(program), 以便CPU可以根據中間的結果來修改後續指令,此理論模型影響後來電腦架構至今。

分類練習: (1) 補充資料:

自我評量:

|

- John von Neumann. Centre for computing history.http://www.computinghistory.org.uk/det/3665/John-von-Neumann/

- http://linux.vbird.org/linux_basic/0105computers.php#ps6

- https://mitpress.mit.edu/books/john-von-neumann-and-origins-modern-computing

- http://w3.salemstate.edu/~tevans/VonNeuma.htm#John_Von_Neumann

- RISC(精簡指令集) vs CISC(複雜指令集),誰更好 http://blog.udn.com/weiyi65/5260959